TMC RESEARCH CORPORATION

TI6VGA (VER. 1.0A)

| Device Type | Mainboard |

| Processor | Celeron/Pentium II |

| Processor Speed | 233/266/300/300A/333/400/450MHz |

| Chip Set | VIA |

| Audio Chip Set | Creative Labs Inc. |

| Maximum Onboard Memory | 384MB (EDO & SDRAM supported) |

| Cache | 0/128/256/512KB (located on the CPU) |

| BIOS | Award |

| Dimensions | 305mm x 200mm |

| I/O Options (backplane) | 32-bit PCI slots (4), floppy drive interface, game port, IDE interfaces (2), parallel port, PS/2 mouse port, serial ports (2), IR connector, USB port, ATX power connector, AGP slot, line in, line out, microphone in, audio in - CD-ROM (2), Wake-on-LAN connector |

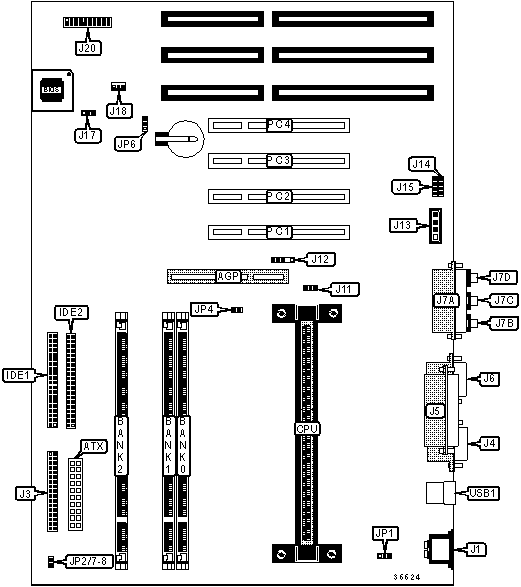

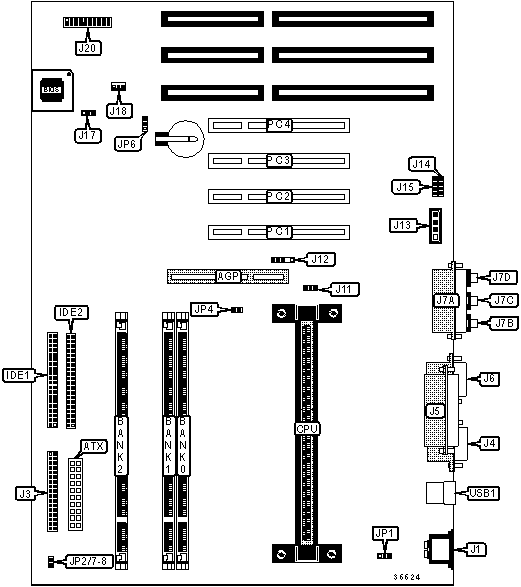

CONNECTIONS |

|||

| Purpose | Location |

Purpose | Location |

| AGP slot | AGP |

Audio in - CD-ROM | J13 |

| ATX power connector | ATX |

Audio in - CD-ROM | J14 |

| IDE interface 1 | IDE1 | Unidentified | J15 |

| IDE interface 2 | IDE2 | Wake-on-LAN connector | J17 |

| PS/2 mouse port | J1 | Chassis fan power | J18 |

| Floppy drive interface | J3 | Speaker | J20/Pins 1 - 4 |

| Serial port 1 | J4 | Power LED & keylock | J20/Pins 11 - 15 |

| Parallel port | J5 | Unidentified | J20/Pins 6 & 16 |

| Serial port 2 | J6 | ATX power on switch | J20/Pins 7 & 17 |

| Game port | J7A | Turbo LED connector | J20/Pins 8 & 18 |

| Line out | J7B | Reset switch | J20/Pins 9 & 19 |

| Line in | J7C | IDE interface LED | J20/Pins 10 & 20 |

| Microphone in | J7D | 32-bit PCI slots | PC1 - PC4 |

| CPU fan power | J11 | USB port | USB1 |

| IR connector | J12 | ||

USER CONFIGURABLE SETTINGS |

|||

Function |

Label |

Position |

|

| Set SDRAM CPU clock | JP2/7 - 8 | Open | |

|

Set SDRAM AGP clock | JP2/7 - 8 |

Closed |

| » | Host frequency autodetected | JP4 | Closed |

| Host frequency at 100 MHz | JP4 | Open |

|

» |

CMOS memory normal operation | JP6 |

Pins 1 & 2 closed |

| CMOS memory clear | JP6 |

Pins 2 & 3 closed |

|

| DIMM CONFIGURATION | |||

Size |

Bank 0 |

Bank 1 |

Bank 2 |

8MB |

(1) 1M x 64 |

None |

None |

16MB |

(1) 1M x 64 |

(1) 1M x 64 |

None |

16MB |

(1) 2M x 64 |

None |

None |

24MB |

(1) 1M x 64 |

(1) 1M x 64 |

(1) 1M x 64 |

32MB |

(1) 2M x 64 |

(1) 2M x 64 |

None |

32MB |

(1) 4M x 64 |

None |

None |

32MB |

(1) 2M x 64 |

(1) 1M x 64 |

(1) 1M x 64 |

48MB |

(1) 2M x 64 |

(1) 2M x 64 |

(1) 2M x 64 |

48MB |

(1) 4M x 64 |

(1) 1M x 64 |

(1) 1M x 64 |

64MB |

(1) 4M x 64 |

(1) 4M x 64 |

None |

64MB |

(1) 8M x 64 |

None |

None |

64MB |

(1) 4M x 64 |

(1) 2M x 64 |

(1) 2M x 64 |

80MB |

(1) 8M x 64 |

(1) 1M x 64 |

(1) 1M x 64 |

96MB |

(1) 4M x 64 |

(1) 4M x 64 |

(1) 4M x 64 |

96MB |

(1) 8M x 64 |

(1) 2M x 64 |

(1) 2M x 64 |

128MB |

(1) 8M x 64 |

(1) 8M x 64 |

None |

128MB |

(1) 16M x 64 |

None |

None |

128MB |

(1) 8M x 64 |

(1) 4M x 64 |

(1) 4M x 64 |

144MB |

(1) 16M x 64 |

(1) 1M x 64 |

(1) 1M x 64 |

160MB |

(1) 16M x 64 |

(1) 2M x 64 |

(1) 2M x 64 |

192MB |

(1) 8M x 64 |

(1) 8M x 64 |

(1) 8M x 64 |

192MB |

(1) 16M x 64 |

(1) 4M x 64 |

(1) 4M x 64 |

256MB |

(1) 16M x 64 |

(1) 16M x 64 |

None |

256MB |

(1) 16M x 64 |

(1) 8M x 64 |

(1) 8M x 64 |

384MB |

(1) 16M x 64 |

(1) 16M x 64 |

(1) 16M x 64 |

| Note: Board supports EDO & SDRAM memory. This board will have 2 Dimm sockets or 2 Dimm sockets; 64MB in place of the 3rd Dimm socket. | |||

CACHE CONFIGURATION |

| Note: 256KB/512KB cache is located on the Pentium II CPU. 128KB cache is located on the Celeron 300A and greater CPUs. |